- • English

- • Русский язык

* Please refer to the English Version as our Official Version.

* Please refer to the English Version as our Official Version.

Ansenmei's SiC JFET with excellent RDS (on) * A performance is particularly suitable for applications that require high current processing capability and lower switching speed, such as solid-state circuit breakers and high current switching systems. Thanks to the excellent material properties of silicon carbide (SiC) and the efficient structure of JFET, lower on resistance and better thermal performance can be achieved, making it very suitable for applications that require multiple devices in parallel to efficiently manage high current loads.

Overview of SiC Combo JFET Technology

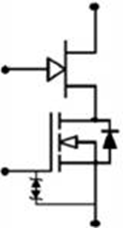

For applications that require normally off devices, low-voltage silicon (Si) MOSFETs can be used in series with normally on silicon carbide (SiC) JFETs to create a cascode structure. In this setup, SiC JFET is responsible for handling high voltage, while Si MOSFET provides normally off functionality. This combination fully utilizes the high performance of SiC JFET and the easy control advantages of Si MOSFET.

The Anson Combo JFET integrates a SiC JFET and a low-voltage Si MOSFET into one package, which not only meets the requirements of small size, but also has high-performance normally off characteristics. In addition, through various gate drive configurations, the Combo JFET also provides advantages such as gate drive compatibility with silicon devices with 5V thresholds, higher reliability, and simplified speed control.

Product Introduction

Combo JFET integrates a SiC JFET and a low-voltage Si MOSFET into one package, and both SiC JFET and low-voltage MOSFET gates can be used.

Figure 1 Combo JFET Structure

Due to the fact that both JFET and low-voltage MOSFET gates can be used, Combo JFET has multiple advantages. These advantages include reduced RDS (on) during overdrive, simplified gate drive circuit through external cascode, adjustable switch speed through JFET gate resistance, and monitoring JFET junction temperature by measuring gate source voltage drop.

Ansenmei SiC Combo JFET Product Series

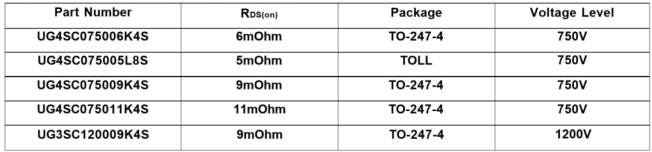

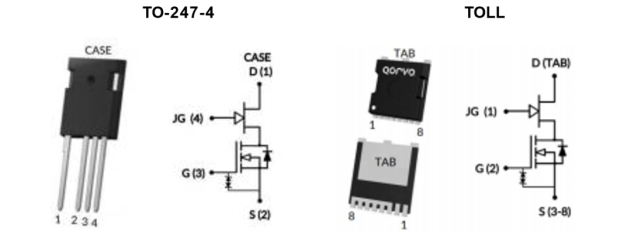

Table 1 and Figure 2 show the Combo JFET products and available packages.

Table 1 Combo JFET Product List

Figure 2 Combo JFET packaging and schematic diagram

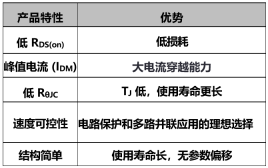

Characteristics and advantages of Ansenmei SiC Combo JFET devices

Table 2 summarizes the characteristics and advantages of ON Semiconductor SiC Combo JFET devices

Table 2 Characteristics and advantages of Ansenmei SiC Combo JFET

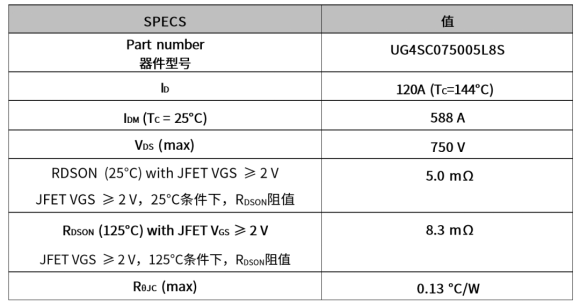

The static characteristics evaluated in this section include RDS (on), peak current (IDM), and R θ JC (thermal resistance from node to shell). For circuit protection and multi-channel parallel applications, dv/dt controllability is crucial. Taking the 750V 5mOhm TOLL package (UG4SC075005L8S) device as an example, evaluate its static and dynamic characteristics.

static characteristic

As shown in Table 3, Anson's advanced SiC JFET technology has achieved excellent electrical and thermal performance in the market.

Table 3 Main Parameters of Anson Mei Combo JFET

The Anson Combo JFET has low RDS (on), high IDM, and low thermal resistance characteristics.

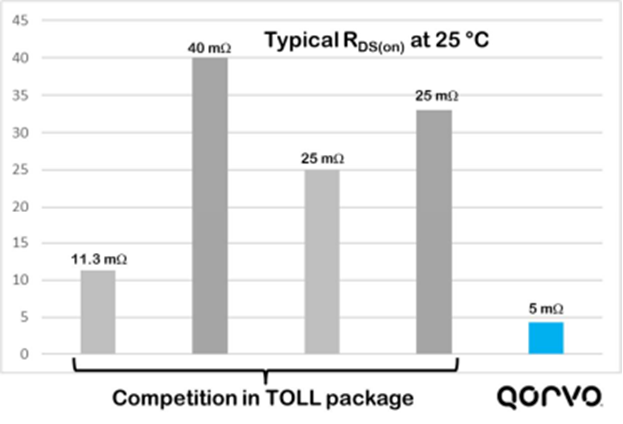

Low RDS (on): Anson Mei Combo JFET devices use SiC JFET technology, which significantly reduces RDS (on) per unit area (Rds? A). The device adopts a flexible and externally configurable cascode structure (SiC Combo FET) to achieve normally off operation. In the Anson Mei SiC Combo JFET structure, the contribution of low-voltage Si MOSFET to the total RDS (on) is less than 10%. Figure 1 shows a comparison of RDS (on) in TOLL packaging.

Comparison of RDS (on) encapsulated in TOLL in Figure 3

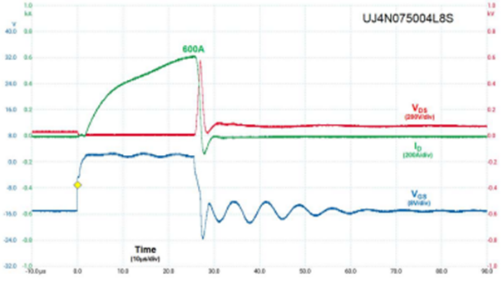

Higher IDM: Peak current is crucial for circuit protection applications, and high IDM SiC Combo JFET is the ideal choice to achieve this goal. Circuit protection applications require robustness and high current ride through capability due to their specific operating conditions.

Figure 4 ID of JFET packaged with Combo JFET

Low R θ JC: Anson's SiC Combo JFET uses silver sintered die attach technology, which improves the interfacial thermal conductivity by six times compared to most soldering materials, achieving the same or even lower junction to shell thermal resistance (R θ JC) at smaller die sizes. Low R θ JC helps maintain a lower junction temperature and ensures higher reliability.

Dynamics

By adjusting the gate resistance of the JFET in the Combo JFET configuration, excellent speed controllability can be achieved, resulting in the following advantages:

·By reducing the shutdown speed to minimize voltage overshoot, circuit protection, especially short-circuit protection, can be strengthened.

·Easy to parallelize, achieving an excellent balance between switch losses and dynamic current balance.

power cycling

The reliability and lifespan assessment of power devices are crucial for improving system reliability and extending service life, especially for emerging wide bandgap (WBG) semiconductors such as SiC, GaN, etc. The main failure mode of power devices is related to thermal mechanical fatigue (TMF). Power thermal cycling test is an accelerated testing method in which the device under test (DUT) is frequently switched on and off, causing its junction temperature to cyclically change in a controlled manner. This method evaluates the reliability of packaging (wiring, die attach, etc.) by applying thermal mechanical stress. At the same time, it also applies electrical stress to semiconductor die and packaged components (wiring, leads, etc.), which can more accurately simulate temperature gradient changes encountered in practical applications compared to passive temperature cycling testing.

In the stacked structure, the Si MOSFET is located above the SiC JFET, and the power line is connected to the source metallization layer of the Si MOSFET. Due to the lower hardness of silicon compared to silicon carbide, the thermal mechanical stress generated during power cycling is significantly reduced, resulting in a doubling of the power cycling life. In addition, whether it is from Si MOSFET to SiC JFET, or from SiC JFET to heat dissipation pads, silver sintered die attach technology is used, which further enhances reliability compared to the widely used solder die attach technology in SiC discrete devices today.

Gate control method

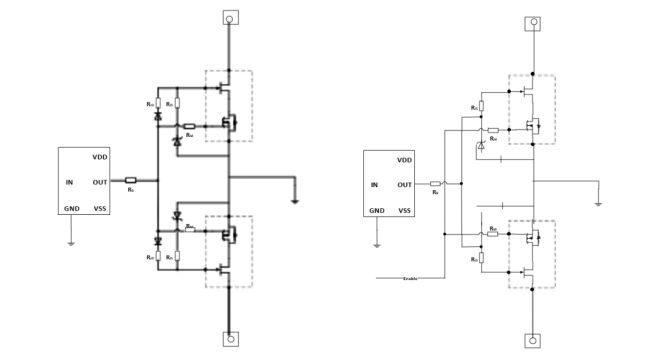

There are two main control methods for Combo JFET used in solid-state circuit breakers: quasi cascode driving mode and direct driving mode.

image.png

Figure 5 Combo JFET driving modes: quasi cascode driving mode (left) and direct driving mode (right)

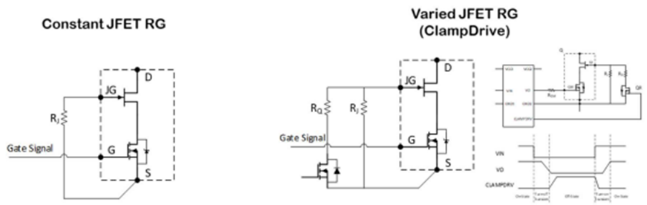

For high-power switch mode applications, in addition to the two control methods shown in Figure 3, we have also developed and recommended the use of ClampDRIVE. Alternatively, the simplest gate control method can be adopted, using a single JFET gate resistor to adjust its switching speed, as shown in Figure 4.

Figure 6 Control method of Combo JFET in switch mode application (left: constant JFET gate resistance, right: ClampDRIVE)

conclusion

Anson Mei SiC Combo JFET has extremely low RDS (on) and controllable switching speed, which can achieve excellent efficiency and power density for circuit breakers and high-power low switching speed applications. It also has power cycling performance (reliability and lifespan) comparable to silicon devices, more than twice as high as SiC MOSFETs.

This is reported by Top Components, a leading supplier of electronic components in the semiconductor industry

They are committed to providing customers around the world with the most necessary, outdated, licensed, and hard-to-find parts.

Media Relations

Name: John Chen

Email: salesdept@topcomponents.ru